集成電路設計 從概念到芯片的精密旅程

集成電路,作為現代電子設備的核心,其設計過程是一項融合了抽象構思與物理實現的復雜系統工程。從最初的一個想法,到最終封裝在設備中的微小芯片,集成電路設計遵循著一套嚴謹、分層、且高度自動化的流程。本文將系統性地介紹這一流程的關鍵階段與核心思想。

一、系統定義與架構設計

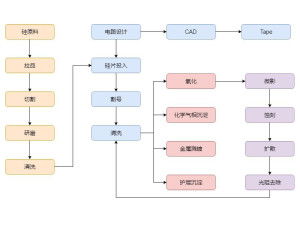

這是設計的起點。設計團隊首先需要明確芯片的功能、性能指標(如速度、功耗、面積)、目標應用場景(如手機、汽車、數據中心)以及成本預算。在此基礎上,進行系統級架構設計,將復雜功能劃分為若干可管理的功能模塊(如處理器核、內存控制器、外設接口等),并定義這些模塊之間的通信協議和數據流。這一階段的輸出通常是高級別架構規格文檔和算法模型。

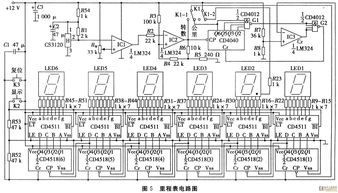

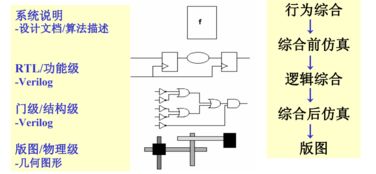

二、邏輯設計(前端設計)

此階段將架構轉化為具體的數字邏輯。設計師使用硬件描述語言(HDL),如 Verilog 或 VHDL,來描述芯片各個模塊的行為和功能。這個用代碼描述的模型被稱為寄存器傳輸級(RTL)設計。通過功能仿真(Simulation)和形式驗證(Formal Verification)來確保RTL代碼的行為完全符合最初定義的規格,糾正邏輯錯誤。邏輯綜合(Logic Synthesis)是此階段的關鍵步驟,它利用電子設計自動化(EDA)工具,將RTL代碼自動轉換為由基本邏輯門(如與門、或門、非門)和觸發器組成的門級網表(Gate-level Netlist),并初步考慮時序和面積約束。

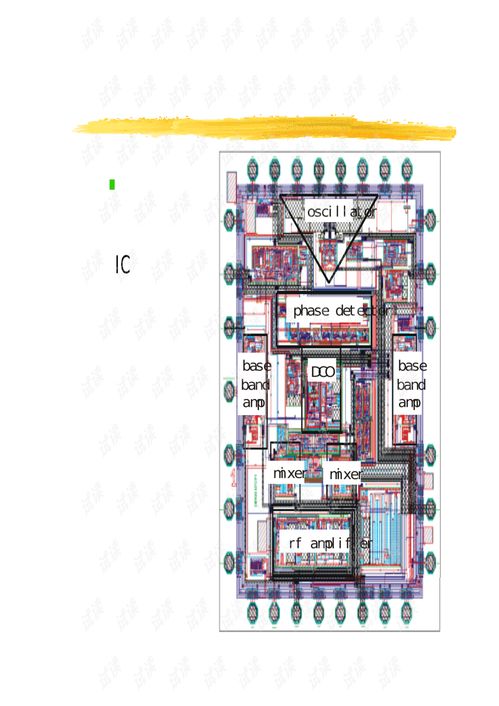

三、物理設計(后端設計)

這是將邏輯網表轉化為具體物理版圖的階段,充滿了幾何與物理的挑戰。主要步驟包括:

- 布圖規劃(Floorplanning):確定芯片核心區域的大小、形狀,以及各個功能模塊(宏單元、存儲器等)在芯片上的大致位置和電源網絡規劃。

- 布局(Placement):將綜合后產生的數百萬甚至數十億個標準單元(邏輯門)精確地放置在芯片版圖的特定位置上,目標是優化連線長度、時序和功耗。

- 時鐘樹綜合(Clock Tree Synthesis,CTS):構建一個低偏移、低延遲的全局時鐘分布網絡,確保時鐘信號能夠幾乎同時到達所有時序單元(觸發器)。

- 布線(Routing):根據布局結果,在多個金屬層上完成所有單元之間實際互連線的繪制。這需要遵循嚴格的制造設計規則(Design Rules)。

- 物理驗證與簽核(Physical Verification & Sign-off):對完成的版圖進行一系列嚴苛檢查,包括設計規則檢查(DRC)、電氣規則檢查(ERC)、版圖與原理圖一致性檢查(LVS),以及最終的時序、功耗和信號完整性分析。只有通過所有簽核,設計才能交付制造。

四、制造、封裝與測試

通過驗證的版圖數據(通常為GDSII格式)被送至晶圓代工廠(Foundry)進行光刻、刻蝕、離子注入等工藝制造,形成晶圓上的裸片(Die)。裸片經過切割、封裝(Package),成為獨立的芯片。必須對封裝后的芯片進行嚴格的量產測試,篩選出功能、性能合格的產品。

貫穿始終的設計驗證

需要強調的是,驗證(Verification)并非一個獨立的階段,而是貫穿于整個設計流程。從行為級模型仿真、RTL功能驗證、到門級時序仿真、以及后端的物理和時序驗證,其工作量往往占到整個設計項目的70%以上,是確保芯片設計一次成功(First Silicon Success)的關鍵。

****

集成電路設計流程是一個典型的“自頂向下設計,自底向上驗證”的迭代過程。它高度依賴先進的EDA工具、精密的設計方法學以及跨領域的專業知識(系統、算法、電路、物理、工藝)。隨著工藝節點不斷微縮至納米尺度,設計面臨的功耗、時序、噪聲和制造變異等挑戰日益嚴峻,這使得整個設計流程更加復雜和協同,持續推動著設計技術與工具的革新。

如若轉載,請注明出處:http://m.rftyn168.com.cn/product/72.html

更新時間:2026-04-08 14:44:48